SiTime product categories

Featured Products

SiTime news

Our stories, product news, media releases and other articles will keep you up to date. Subscribe to our newsletter or follow us on LinkedIn.Go to SE Magazine

15.12.2025

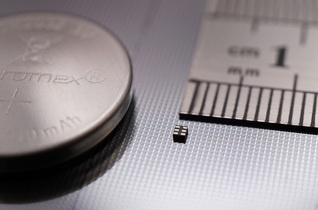

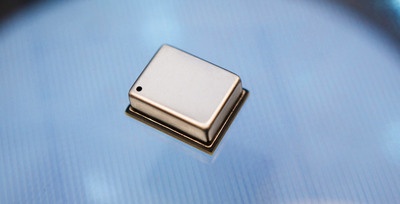

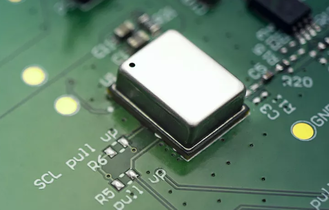

SiTime: low power, small footprint - Sensor Clock Source SiT1605 Oscillator

The SiTime® SiT1605 oscillator delivers precise, reliable clocking in an ultra-small, low-power design—making it ideal for today’s space- and energy-constrained sensor applications. It provides consistent performance to help extend battery life while enab

26.09.2024

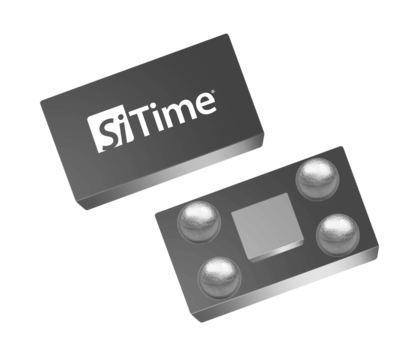

SiTime: SiT1811 32kHz XO with Low Power and Small Footprint

The SiTime SiT1811 is an ultra-low-power 32.768 kHz MEMS-based oscillator (XO), designed for consumer applications that prioritize battery efficiency, reliability, and compact size. It operates at less than 0.6 µW of power, significantly reducing energy c

24.04.2024

SiTime: EPOCH gets Awarded for Embedded Computing Design’s Best in Show at Embedded World 2024

The Embedded Computing Design team has honored SiTime's Epoch Platform with the prestigious Best in Show award in the MEMS & Sensors category for the Embedded World 2024

23.02.2024

SiTime: AI Semiconductors - Why the Future is Coming faster than you think

They are in supercomputers, crunching large data sets to understand mega patterns, probabilities and outcomes. They help us understand the origins of the universe, combat climate change, and aid in the development of new medicines

06.02.2024

SiTime: Why MEMS Precision Timing Upstages Quartz for Automotive Reliability and Safety

Automotive innovation is rapidly advancing, shifting toward next-generation vehicles that are not only greener, more efficient and higher performing but also safer and more reliable. Much like a human heartbeat, timing components in automotive application

11.01.2024

SiTime: Consumer Tech Enthusiasts Test Drive the Future of Automotive at CES 2024

Today’s cars are the ultimate consumer machines. The modern automobile embodies unlimited mobility, cutting-edge connectivity, and more street smarts than ever while going the distance to keep us safe and comfortable.

28.09.2023

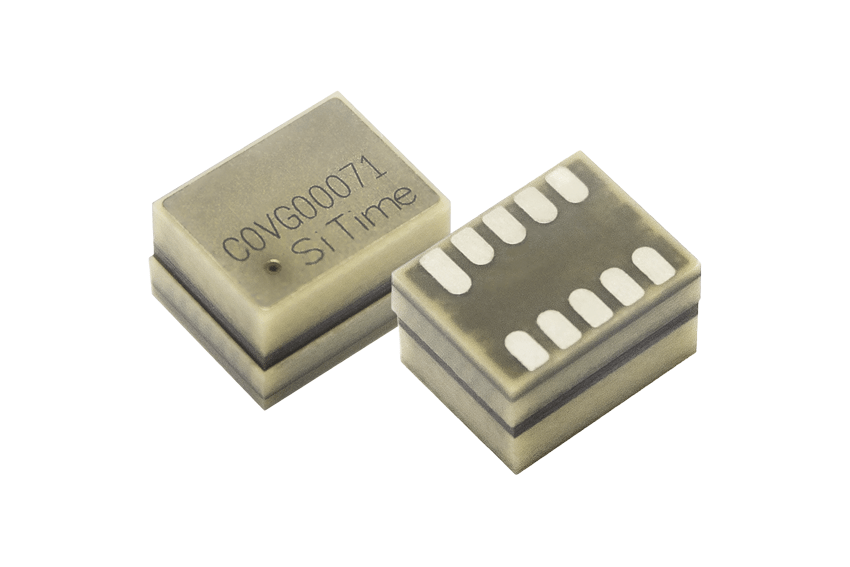

SiTime: Epoch Platform, OCXO, REIMAGINING THE HOLDOVER OSCILLATOR

Epoch Platform OCXOs exhibit remarkable resilience to thermal shock, airflow, and vibration

11.11.2022

SiTime setzt mit neuem Präzisionsoszillator für Rechenzentren und 5G-Infrastruktur neue Maßstäbe bei der Timing-Leistung

Unerreichte Kombination aus 30-fach höherer Zuverlässigkeit, 4-fach geringerer Größe und 4-fach geringerem Stromverbrauch

19.10.2022

SiTime erweitert das Oszillatorportfolio mit einer neuen Familie von Präzisions-Timing-Lösungen, die SiT1881 Familie

SiTime hat heute eine neue Familie von 32-kHz-Oszillatoren mit extrem niedrigem Stromverbrauch vorgestellt.

28.04.2020

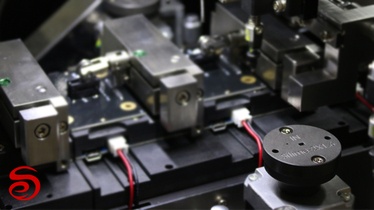

SE Spezial-Electronic offers a unique service for oscillators available for immediate delivery.

Series quantities can thus be programmed at any time within 24 hours.

Do you have questions about SiTime?

Feel free to contact us via our chat function,via our contact form or by phone!

SE Spezial-Electronic GmbH

Friedrich-Bach-Straße 1

D - 31675 Bückeburg

T +49 5722 203-0

F +49 5722 203-120

info@spezial.com