CML product categories

Featured Products

CML Micro news

Our stories, product news, media releases and other articles will keep you up to date. Subscribe to our newsletter or follow us on LinkedIn.Go to SE Magazine

21.12.2024

CMX90A003 1W 860 – 960 MHz Power Amplifier

The CMX90A003 is a two-stage, fully matched MMIC PA delivering +29.5 dBm of saturated power for use in the 860 – 960 MHz frequency range, applicable to license-free bands.

24.09.2024

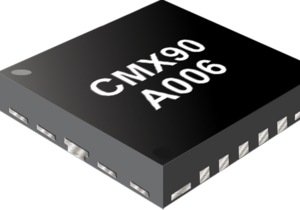

CML launches sub-GHz band GaAs 2W linear power amplifier to ease UHF system development

CML Micro extends its SµRF range of sub-GHz MMICs with a 2 W power amplifier optimized for linear performance and high reliability. The CMX90A006 is intended as a final-stage ISM (915 MHz) and SRD (868 MHz) band power amplifier in wireless transmitter...

18.06.2024

CML Micro launches the CMX90A705

CML Micro launches the CMX90A705, a Ka-band gallium nitride (GaN) power amplifier that represents a cost-effective building block for commercial high-volume satellite communication terminals.

20.05.2024

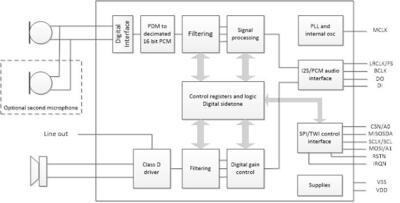

DRM1000 - The world's most versatile DRM Receiver

CML Micro has today announced the global availability of the DRM1000 module - a complete Digital Radio Mondiale (DRM) broadcast receiver implementation that will enable consumer radio manufacturers to connect communities with low-cost...

26.01.2024

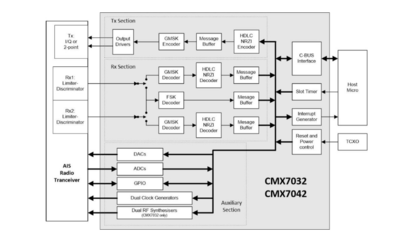

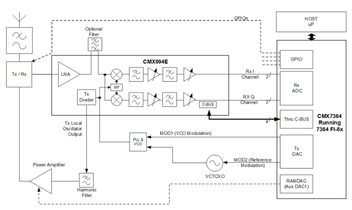

Wireless Data Baseband Solution supports SC135, the latest Real Time Kinematics Communications standard

CML Micro is addressing this solution by offering a firmware upgrade to its CMX7364 Multi-mode High Performance Wireless Data Modem, the 7364FI-8.

31.03.2023

CML Micro launch the CMX90B701/702 low current mmWave gain blocks

The new additions to the SµRF product family are the latest to leverage CMLs innovative RFIC/MMIC design capability, offering low current and low noise performance in the 17 – 23 GHz and 23 – 29.5 GHz ranges respectively.

28.09.2022

CML announce the launch of the CMX90G301 & CMX90G302 Low-power Cascadable Gain Blocks

With positive gain-slopes of +1dB and +2dB respectively, and an operating frequency range of 1.4 – 7.1 GHz, both devices are ideally suited to a range of RF applications, including 4G/5G infrastructure and devices operating in unlicensed frequency bands.

21.06.2022

CML announce the launch of the CMX90A702 28 GHz 5G Medium Power Amp

The latest product to be developed using CMLs new SµRF RFIC/MMIC design capability, the CMX90A702 MPA targets 5G mmWave infrastructure applications...

Do you have questions about CML?

Feel free to contact us via our chat function,via our contact form or by phone!

SE Spezial-Electronic GmbH

Friedrich-Bach-Straße 1

D - 31675 Bückeburg

T +49 5722 203-0

F +49 5722 203-120

info@spezial.com