SiT95315 - Quad PLL, 12-output Jitter Cleaner

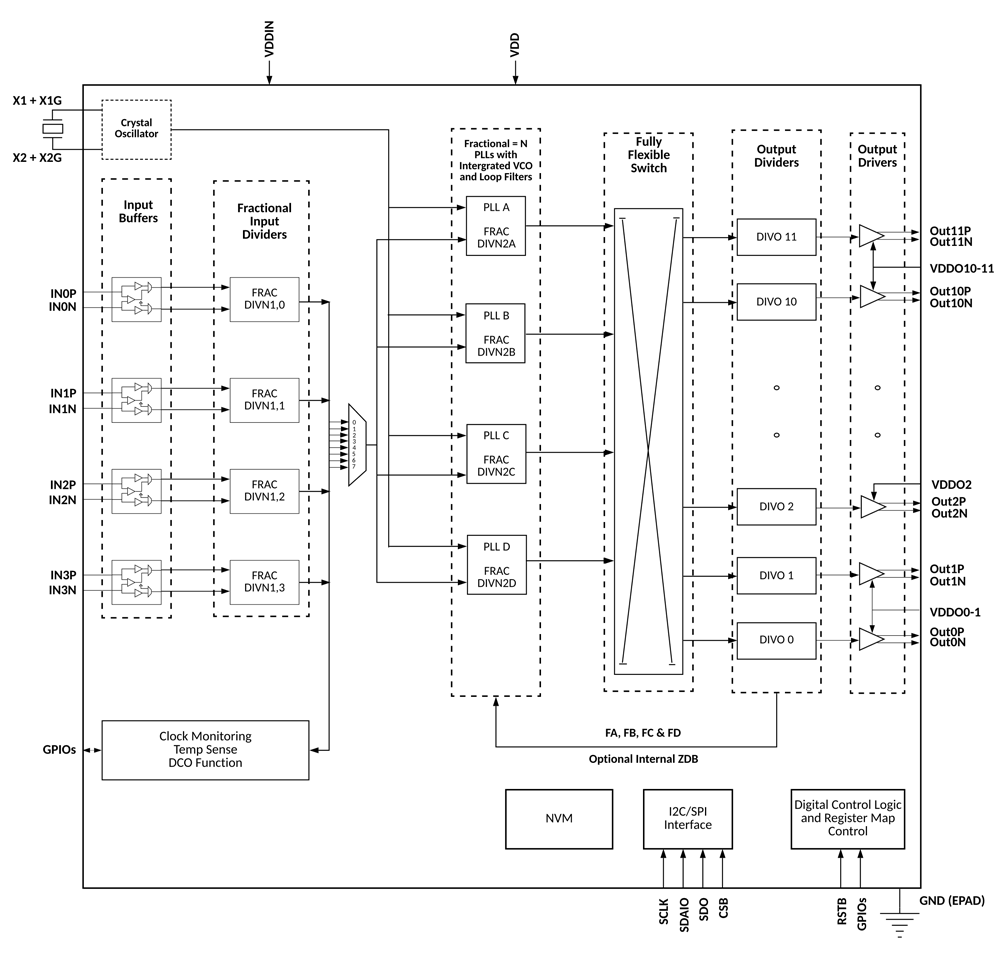

The SiT95315 offers programmable quad fractional frequency translation based jitter cleaning with flexible input to output frequency translation options. The high performance DPLLs support up to 4 differential or 8 single-ended input clocks and provide 12 clock outputs. The clock outputs can be derived from any of the 4 PLLs in a fully flexible manner. This device is fully programmable with the I2C/SPI interface or an on-chip one time (OTP) programmable non-volatile memory for factory pre-programmed devices.

The SiT95315 offers programmable quad fractional frequency translation based jitter cleaning with flexible input to output frequency translation options. The high performance DPLLs support up to 4 differential or 8 single-ended input clocks and provide 12 clock outputs. The clock outputs can be derived from any of the 4 PLLs in a fully flexible manner. This device is fully programmable with the I2C/SPI interface or an on-chip one time (OTP) programmable non-volatile memory for factory pre-programmed devices.

| Operating Temperature Range (°C) | -40 to 85 |

| Package Type (mm²) | 9x9 mm, 64-pin QFN |

| Number of Inputs | 4 |

| Number of Outputs | 12 |

| Input Type | LVCMOS, LVDS, LVPECL, CML |

| Input Frequency Range | 8 kHz to 2.1 GHz (Differential) |

| Output Type | LVPECL , CML , HCSL , LVDS , LVCMOS |

| Output Frequency Range | 0.5 Hz to 2.94912 GHz (Differential) |

| Number of PLL/Clock Domains | 4 PLL |

| Phase Jitter (rms) | 85 fs typ.; 70 fs typ. (with MEMS oscillator) |

| Repeatable Input-Output Delay | ±225 ps |

| Frequency Control DCO | 0.001 ppt (all outputs) |

| Phase Control DCO | <1 ps (all outputs) |

| Internal ZDB Mode | <0.5 ns input to output delay variation |

| Programmability | NVM OTP, External EEPROM, Partial autonomous, SPI/I2C |

| Features | Wander attenuation loop bandwidth down to 0.09 mHz, ±25 ps maximum phase hit, JESD204B/C support |

Block Diagramm SiT95315:

| Number of Outputs: | 12 |

|---|---|

| Number of Inputs: | 4 |